2023年04月高等教育自学考试 计算机系统结构答案

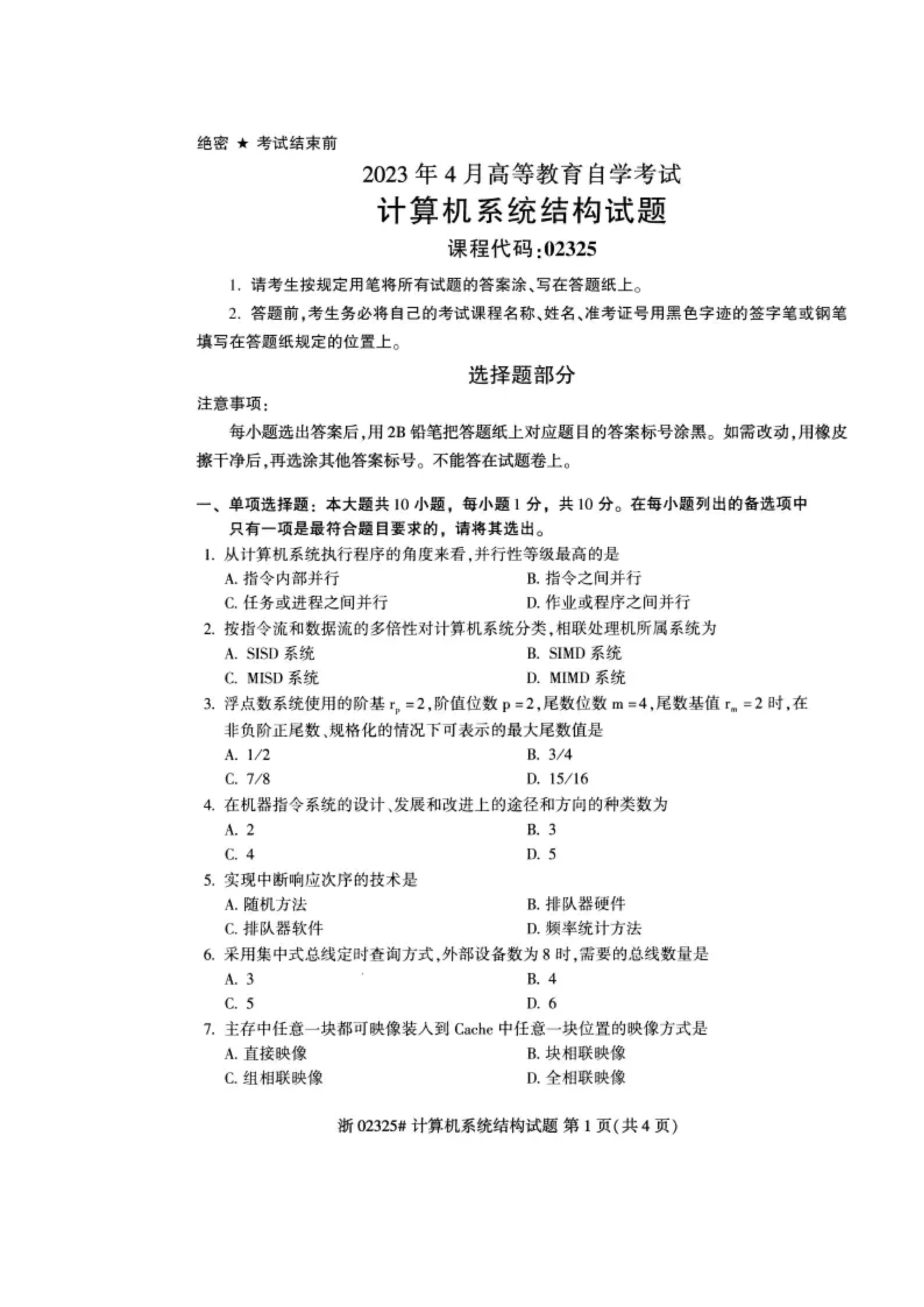

一、单项选择题:本大题共10小题,每小题1分,共10分。在每小题列出的备选项中只有一项是最符合题目要求的,请将其选出。

1、D

从算机系统执行程序的角度来看,并行性等级由低到高可分为四级。分别是:①②指令之间——多条指令的并行执行。③任务或进程之间——多个任务或程序段的并行执行。④作业或程序之间——多个作业或多道程序的并行执行。P47

2、B

SIMD系统如图1-11b所示,具有代表性的例子是阵列处理机和相联处理机。如果把 “多倍性”定义中的“处于同一执行阶段”理解为一条指令的操作全过程,则流水线处理 机也可包括在内。P51

3、D

4、A

5、B

中断响应用排队器硬件实现 可以加快响应和断点现场的保存,中断处理釆 用软的技术可以提供很大的灵活性。P107

6、C

7、D

在全相联映像中,主存中的任何一块都可以映射到Cache中的任何一个位置,因此它具有最大的灵活性和最小的冲突。但是,由于需要比较所有Cache块的标记来确定是否命中,因此全相联映像的访问时间较长。

8、D

指令相关、访存操作数相关和通用寄存器组数相关等局部性相关都是由于在机器同时 解释的多条指令之间出现了对同一主存单元或寄存器要求“先写后读”。重叠机器处理这 些局部性相关的方法有两种。一种是推后后续指令对相关单元的读,直至在先的指令写入 完成;另一种是设置相关直接通路,将运算结果经相关直接通路直接送入所需部件。P185

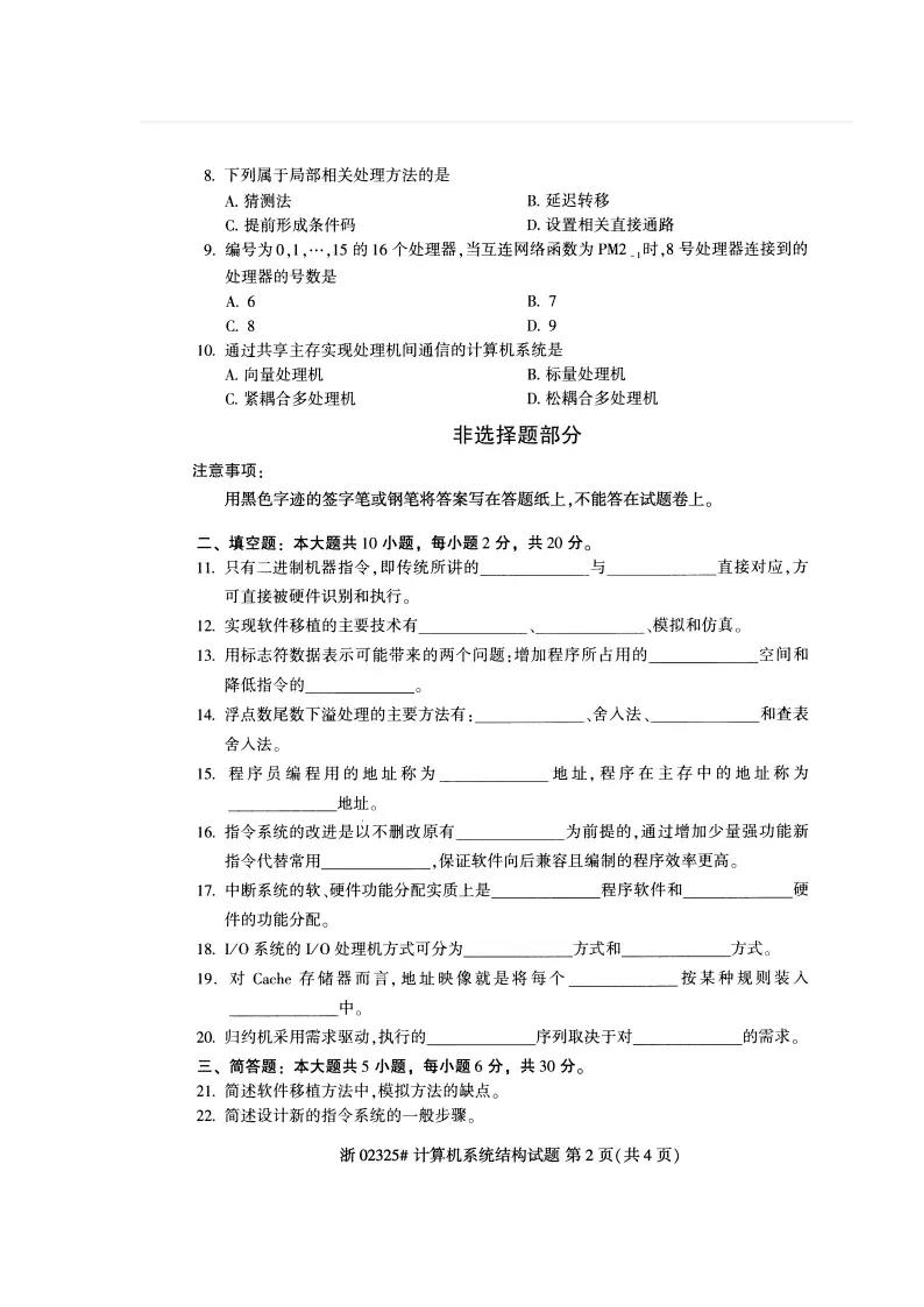

9、A

10、C

紧耦合多处理机是通过共享主存实现处理机间通信的,其通信速率受限于主存频宽。 各处理机与主存经互连网络连接,处理机数受限于互连网络带宽及各处理机访主存冲突的概率。P238

二、填空题:本大题共10小题,每小题2分,共20分。

11、机器语言、机器硬件

12、统一高级语言、采用系列机(次序可更改)

13、主存、执行速度

14、截断法、恒置“1”法(次序可更改)

15、逻辑、物理

16、指令系统、指令串

17、中断处理、中断响应

18、通道、外围处理机(次序可更改)

19、主存块、高速缓冲存储器(或Cache)

20、操作、数据

三、简答题:本大题共5小题,每小题6分,共30分

21、答案

模拟程序的编制非常复杂和费时;虚拟机的每条机器指令不能直接被宿主机的硬件执行,需要经相应的由多条宿主机机器指令构成的解释程序来解释,使得模拟的运行速度显著降低,实时性变差。

22、答案

(1)根据应用,初拟出指令的分类和具体的指令;

(2)试编出用该指令系统设计的各种高级语言的编译程序;

(3)对各种算法编写大量的测试程序并进行模拟测试,看指令系统的操作码和寻址方式效能是否都比较高;

(4)将程序中高频出现的指令串复合改成一条强功能的新指令,即改用硬件方式实现;将频度很低的指令的操作改成用基本的指令组成的指令串来完成,即用软件方式实现。

23、答案

(1)简化指令系统设计,适合VISI实现;

(2)提高计算机的执行速度和效率;

(3)降低设计成本,提高系统的可靠性;

(4)可直接支持高级语言的实现,简化编译程序的设计。

24、答案

总线分配速度快,所有部件的总线请求同时送到总线控制器,不用查询;

控制器可以使用程序可控的预定方式、自适应方式、循环方式或它们的混合方式灵活确定下一个使用总线的部件;

能方便地隔离失效部件的请求。

25、答案

(1)结构不要过分复杂,以降低成本;

(2)互连要灵活,以满足算法和应用的需要;

(3)处理单元间信息交换所需要的传送步数要尽可能少,以提高速度性能;

(4)使用规整单一的基本构件组合而成,或者经多次通过或者经多级连接来实现复杂的互连,使模块性好,以便于用VLSI实现并满足系统的可扩充性。

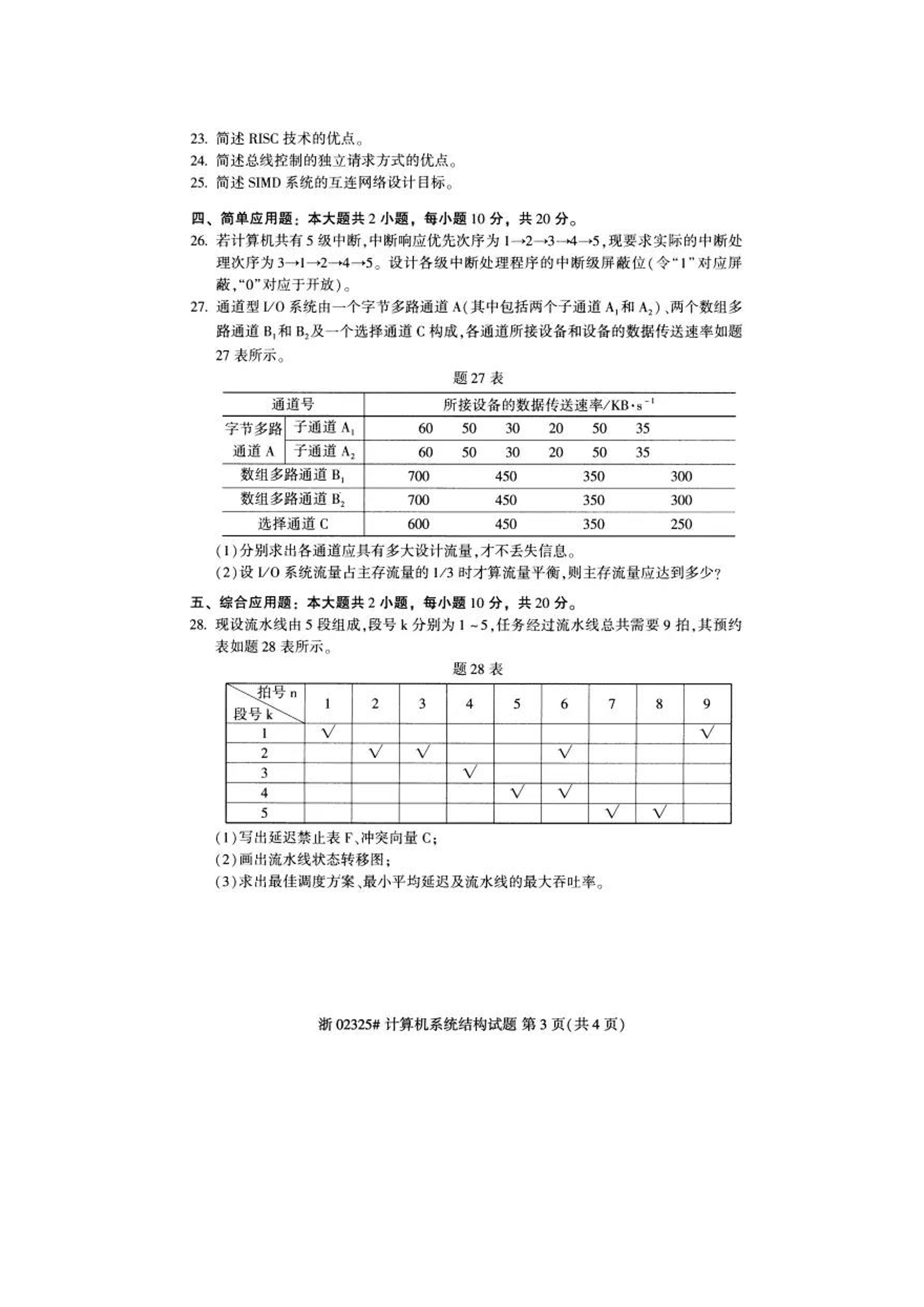

四、简单应用题:本大题共2小题,每小题10分,共20分。

26、答案

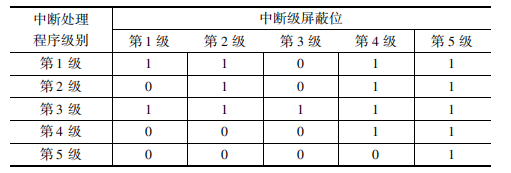

中断程序的中断屏蔽位设置如表所示。

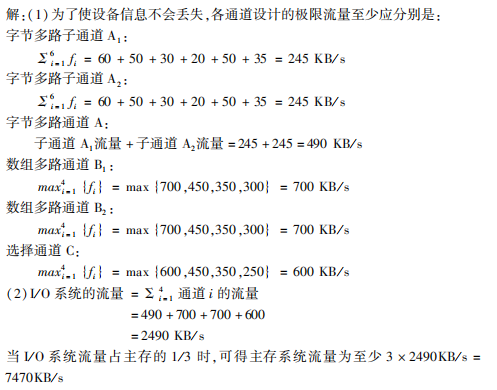

27、答案

五、综合应用题:本大题共2小题,每小题10分,共20分。

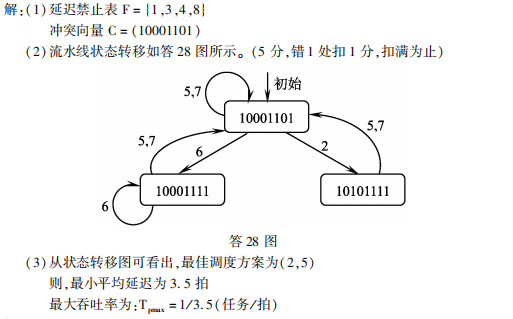

28、答案

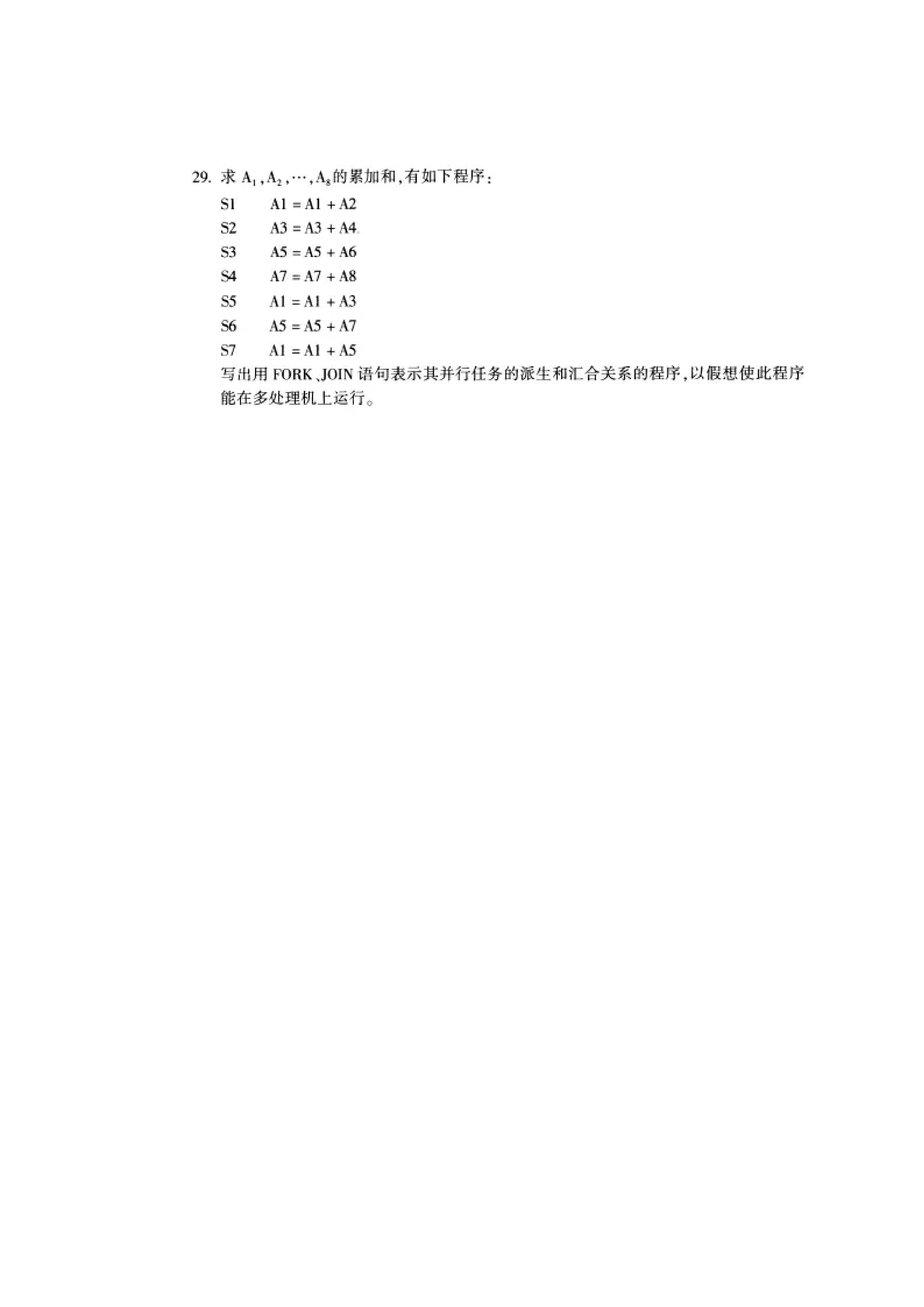

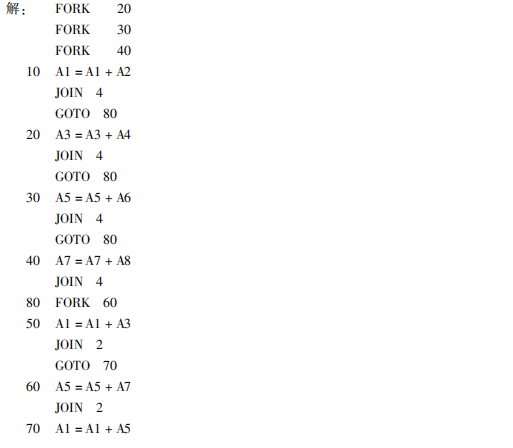

29、答案

《半城明媚半城雨第一季》国产剧高清在线免费观看:https://www.jgz518.com/xingkong/33712.html

1

555

1

1

555